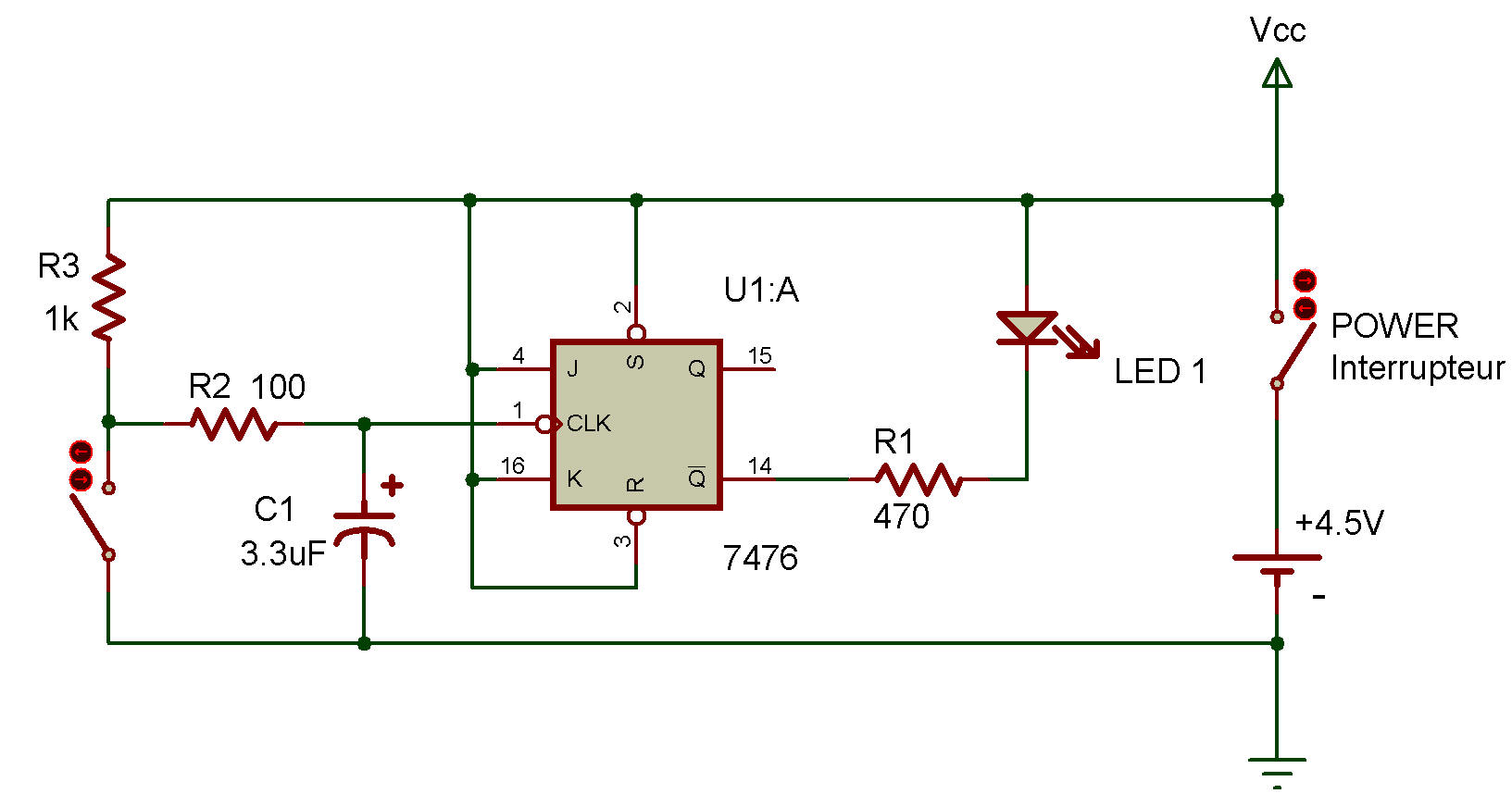

Here, a short time constant circuit along CLK input has been demonstrated, which converts quadrate-type clock pulse into narrow spikes, as has been depicted in the diagram. In figure 5.24, logic diagram of a positive edge triggered JK flip-flop along with its timing diagram has been denoted, wherein two data inputs J and K are also visible besides clock input. It should be kept into mind that both PR and CLR are asynchronous and they invalidate or reject all other operational input signals. This is a negative edge-triggered flip-flop, for which CLR has to be brought low in order to reset it. In figure ©, another commercially available JK flip-flop has been demonstrated. Output Q shows an immediate reaction on PR and CLR signals. Remember that it is a negative edge-triggered flip-flop which requires low PR for being set or low CLR for being reset. The symbol shown in figure (b), represents a JK flip-flop which contains two additional characteristics of preset and clear. When both J and K are high, Q toggle on inverted states When J is high and K is low, Q gets set or becomes high When J is low and K is high, output Q tends to reset or turn low

When both J and K inputs are low, no change occurs in Q Whenever somebody happens to see such a symbol on any circuit diagram, following points will certainly come into mind. The symbol shown in figure (a), represents a symbol for any type of flip-flop. In figure 5.23, various symbols of a JK flip-flop have been depicted. These flip-flops are both positive edge-triggered as well as negative edge-triggered. As this flip-flop possess features of flip-flops of all other types, that is why it is generally known as a universal flip-flop.

It has vastly been used for manufacture of counters. A JK flip-flop is an ideal memory element which can be used for counting purposes. If both inputs of a JK flip-flop are presumed to be set or reset similar to an RS flip-flop, its operation can be understood quite easily (i.e. The operational mechanism of a JK flip-flop is also similar to that of an RS flip-flop, the only difference being that contrary to an RS flip-flop, no invalid state exists in a JK flip-flop. In a JK flip-flop, J & K refer to two inputs, similar to R and S are two inputs in an RS flip-flop. JK flip-flop is a versatile and probably most widely used flip-flop. Besides, another basic difference between the two is that RS flip-flop consists of a single feedback circuit whereas JK flip-flop consists of a double feedback circuit. JK flip-flop consists of three whereas RS flip-flop 2 inputs. However, a difference still exists between a JK flip-flop and an RS flip-flop. JK flip-flop is an amended form of RS flip-flop and it is also free from the defect of race condition (both outputs becoming high at a time is called race condition).

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed